Читайте также:

|

Мікропроцесор Pentium виготовлений за 0,8-мікронною БІКМОН-технологією з комбінованим використанням біполярних транзисторів (для підвищення швидкодії) і КМОН-структур – для зменшення споживаної потужності та збільшення щільності компоновки. Перший процесор Pentium був розрахований на частоти роботи 60 і 66 Мгц, випускався у корпусі типу PGA-273 (матриця 21*21), мав напругу живлення плюс 5 В і споживав потужність 16 Вт.

· Структура мікропроцесора Pentium включає (рис. 7.18):

· виконавчі U- і V -конвейери з АЛП кожний;

· пристрій обчислень з плаваючою комою FPU;

· регістровий файл;

· роздільні кеш команд і кеш даних;

· дешифратор команд і пристрій керування;

· буфери передвибірки з випередженням;

· буфери прогнозування адреси переходів;

· шинний інтерфейс з 64-розрядной ШД.

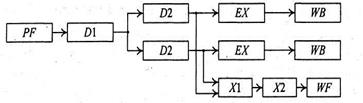

Цілочисельні U- і V -конвейєри мають наступну п'ятиступеневу структуру (рис. 7.19):

· PF (Pre Fetch) – попередня вибірка (передвибірка);

· D1 (Decode Stage1) – декодування команд і визначення можливості запуску на виконання відразу двох команд;

· D2 (Decode Stage2) – генерація адрес операндів;

· EX (Execute) – буфер оберненого запису завершення виконання команди і можлива зміна стану процесора;

· X1, X2, WF – використовуються FPU.

|

Рис. 7.18. Структура мікропроцесора Pentium

Кожний конвеєр має своє АЛП, сукупність пристроїв генерації адрес на ступені D2 з використанням багатоканального суматора і інтерфейсу з кешами.

Рис. 7.19. Конвеєри мікропроцесора Pentium

Процес видачі на виконання одночасно двох команд називається парним запуском; він ніяк не обмежує програмування завдань. Обидва конвеєри функціонально подібні, проте головний U-конвейєр виконує всі цілочисельні операції, а V-конвейєр – тільки прості й деякі команди з плаваючою комою. Конвеєри працюють одночасно, і при парному запуску спочатку в U-конвейєр подається більш складна команда, а потім в V-конвейєр поступає простіша команда. Якщо дві команди запустити не можна, то працює U-конвейєр, а V-конвейєр простоює. Якщо виконання команди зупиняється на будь-якому ступені, то команда в другому конвеєрі зупиняється на тому ж ступені (за окремими виключеннями).

Парні запуски можливі за відсутності залежності між двома командами, наприклад, при зверненні до одного і того ж регістра. Команди FPU не запускаються в парі з цілочисельними командами.

Кожний конвеєр має 64-розрядний буфер записування WB, з якого інформація передається до пам'яті в порядку її генерації процесорним ядром.

Математичний співпроцесор FPU реалізовано на триступінчатому конвеєрі з плаваючою комою, який прибудований до цілочисельного конвеєра. Команди FPU проходять по загальному конвеєру до степені ЕХ, після цього вони проходять по степеніх XI, X2, WE конвеєра FPU. Пристрій FPU підтримує операції з операндами 32-, 64- і 80-розрядного формату.

Для зберігання поточних операндів селекторів сегментів пам'яті та інформації про стан процесора передбачений регістровий файл, який містить вісім загальних регістрів, шість сегментних регістрів і два регістри станів і керування. Окремі кеші команд і даних об'ємом 8 Кбайт кожен виключають конфлікти при одночасному зверненні до команд і даних на стадії попередньої вибірки. Кожен кеш – це два двоканальні асоціативні модулі з довжиною рядка 32 байти і шириною зовнішньої шини 8 байт. Пам'ять кожного кеша розбита на вісім банків з чергуванням по межах в 4 байт. Кеш даних має два інтерфейси, поодинці для кожного конвеєра.

Якщо конвеєрам необхідні дані з різних банків, то вони обслуговуються одночасно в одному такті. З кожним кешем пов'язаний свій асоціативний буфер трансляцій, який перетворює логічні адреси у фізичні.

Інформація в рядках кеша даних має наступні ознаки: модифікована; що належить тільки даному кешу; розподілена з іншими кешами; недійсна. Це забезпечується протоколом MESI (Modified – Exclusive-Shared- Invalid- протокол підтримки когерентності пам'яті за наявності кеша, названий відповідно до станів рядків). Кеш даних може настроюватися на алгоритм крізного або зворотного записування.

Кеш команд захищений від випадкових записувань і його рядки позначаються як загальні з іншими кешами команд або як недійсні.

Блок передвибірки команд має чотири 32-байтові буфери, переходів ВТВ, що працюють разом з буфером адрес (Branch Target Buffer). Вибірка проводиться послідовно до появи команди переходів, після чого блок ВТВ прогнозує – буде перехід чи ні. Наприклад, після виконання кожного програмного циклу (а це може бути сотні разів) обчислюється умова - повернутися на початок циклу або вийти з нього. Ці два рішення (шляхи) називаються прогнозуванням адрес переходів.

Блок ВТВ запам'ятовує адресу і команду першого входження в цикл і передбачає, що з появою команди переходу цикл продовжуватиметься. Якщо прогноз правильний, то перехід виконується без затримки. Інакше використовуються додаткові три-чотири такти для обчислення умов дійсного перекладу і зчитування наступної команди.

Зовнішня шина має 32 лінії адреси або 64 лінії даних, проте усередині обробляються 32-розрядні дані. Ця шина забезпечує можливість пакетних пересилань (швидкість до 528 Мбайт/с) і циклів пакетного узгодження інформації між кешами і ОЗП при використанні алгоритму зворотного записування.

Дата добавления: 2015-10-24; просмотров: 117 | Нарушение авторских прав

| <== предыдущая страница | | | следующая страница ==> |

| Арифметичний співпроцесор К1810ВМ87 | | | Архітектура POWER |